d0iasm / Rvemu For Book

Licence: mit

Reference implementation for the book "Writing a RISC-V Emulator in Rust".

Stars: ✭ 141

Programming Languages

rust

11053 projects

Projects that are alternatives of or similar to Rvemu For Book

riscv em

Simple risc-v emulator, able to run linux, written in C.

Stars: ✭ 51 (-63.83%)

Mutual labels: emulator, riscv

rv32emu

RISC-V RV32I[MAC] emulator with ELF support

Stars: ✭ 61 (-56.74%)

Mutual labels: emulator, riscv

Riscv Rust

RISC-V processor emulator written in Rust+WASM

Stars: ✭ 253 (+79.43%)

Mutual labels: riscv, emulator

Unicorn

Unicorn CPU emulator framework (ARM, AArch64, M68K, Mips, Sparc, PowerPC, RiscV, X86)

Stars: ✭ 4,934 (+3399.29%)

Mutual labels: emulator, riscv

Rvemu

RISC-V emulator for CLI and Web written in Rust with WebAssembly. It supports xv6 and Linux (ongoing).

Stars: ✭ 289 (+104.96%)

Mutual labels: riscv, emulator

Epsxe64ubuntu

Install ePSXe Linux (x64) & shaders using BIOS HLE and Core Plugins on x86-64 Debian, Ubuntu, Linux Mint and their derivatives.

Stars: ✭ 130 (-7.8%)

Mutual labels: emulator

Shibari

Gaming input peripherals test platform for Windows

Stars: ✭ 136 (-3.55%)

Mutual labels: emulator

Retro8

PICO-8 implementation with SDL2 and RetroArch back-ends

Stars: ✭ 116 (-17.73%)

Mutual labels: emulator

Mos6502

A fast & simple MOS 6502 CPU emulator written in C++

Stars: ✭ 135 (-4.26%)

Mutual labels: emulator

V86

x86 virtualization in your browser, recompiling x86 to wasm on the fly

Stars: ✭ 12,765 (+8953.19%)

Mutual labels: emulator

Crylogger

CRYLOGGER: Detecting Crypto Misuses for Android and Java Apps Dynamically

Stars: ✭ 125 (-11.35%)

Mutual labels: emulator

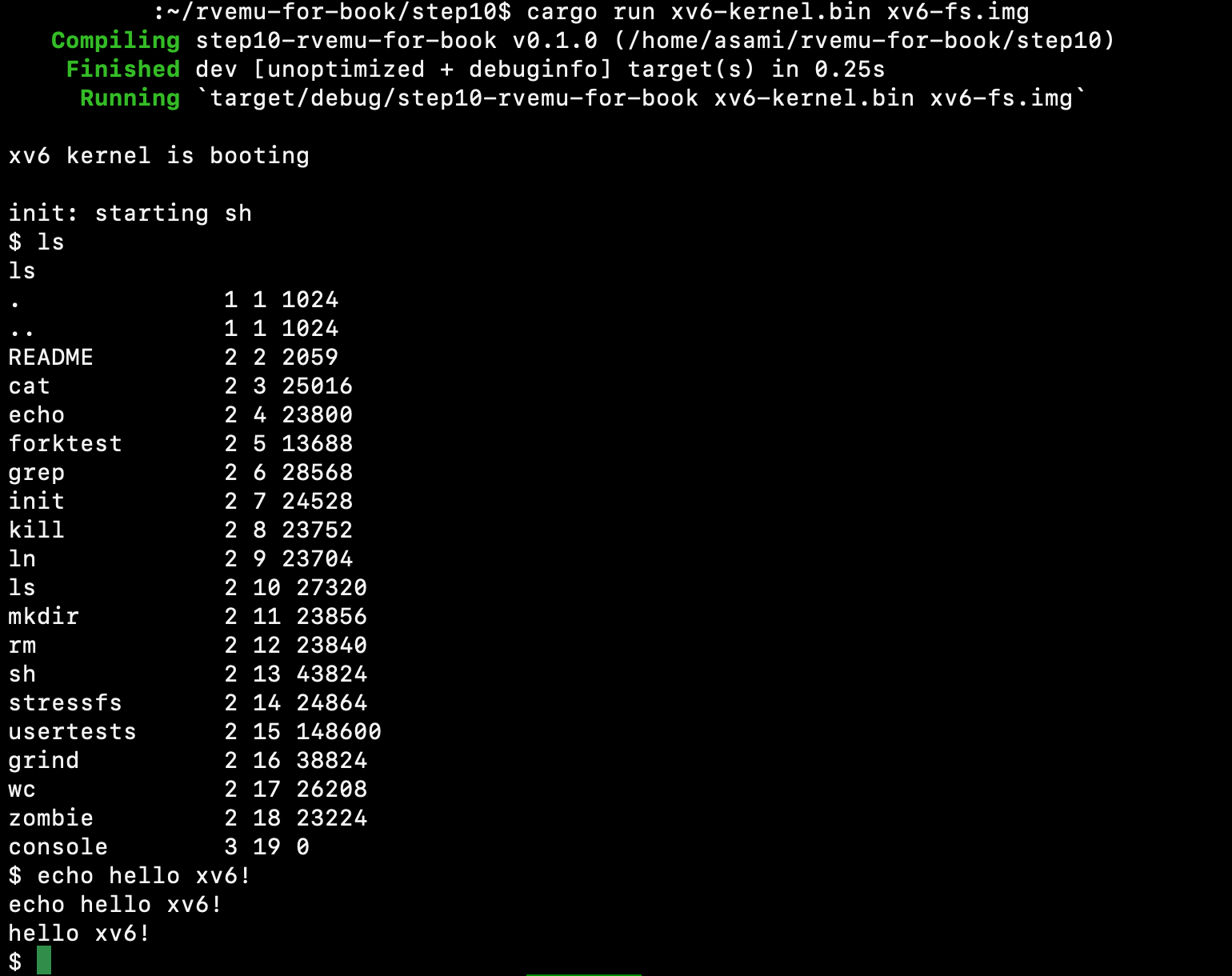

rvemu-for-book

Reference implementation of the book, Writing a RISC-V Emulator from Scratch in 10 Steps. The goal of this code and the book is runnning xv6 in our emulator.

This is based on original RISC-V emulator rvemu in Rust.

How to run xv6

$ cd step10 // move to the step10 directory

$ cargo run ./xv6-kernel.bin ./xv6-fs.img

Step to implement a RISC-V emulator

- Step 1: Setup and Implement Two Instructions

- Step 2: RV64I Base Integer Instruction Set

- Step 3: Control and Status Registers

- Step 4: Privileged Instruction Set

- Step 5: Exceptions

- Step 6: UART (a universal asynchronous receiver-transmitter)

- Step 7: PLIC (a platform-level interrupt controller) and CLINT (a core-local interrupter)

- Step 8: Interrupts

- Step 9: Virtio

- Step 10: Virtual Memory System

Each step has a diff file generated by diff -x target -r step<previous> step<current> > diff_<previous>_<current>.

Note that the project description data, including the texts, logos, images, and/or trademarks,

for each open source project belongs to its rightful owner.

If you wish to add or remove any projects, please contact us at [email protected].