mattvenn / Fpga Sram

mystorm sram test

Stars: ✭ 16

Labels

Projects that are alternatives of or similar to Fpga Sram

Platformio Core

PlatformIO is a professional collaborative platform for embedded development 👽 A place where Developers and Teams have true Freedom! No more vendor lock-in!

Stars: ✭ 5,539 (+34518.75%)

Mutual labels: verilog

Verilog Ethernet

Verilog Ethernet components for FPGA implementation

Stars: ✭ 699 (+4268.75%)

Mutual labels: verilog

Naivecpu

A CPU that implementing THCO-MIPS16 instruction set.

Stars: ✭ 5 (-68.75%)

Mutual labels: verilog

Platformio Vscode Ide

PlatformIO IDE for VSCode: The next generation integrated development environment for IoT

Stars: ✭ 676 (+4125%)

Mutual labels: verilog

Cocotb

cocotb, a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python

Stars: ✭ 740 (+4525%)

Mutual labels: verilog

Netlist Graph

Java library for parsing and manipulating graph representations of gate-level Verilog netlists

Stars: ✭ 7 (-56.25%)

Mutual labels: verilog

Verilator

Verilator open-source SystemVerilog simulator and lint system

Stars: ✭ 645 (+3931.25%)

Mutual labels: verilog

Corundum

Open source, high performance, FPGA-based NIC

Stars: ✭ 577 (+3506.25%)

Mutual labels: verilog

Ie12

A (very) minimal web browser for FPGAs implemented in Verilog

Stars: ✭ 6 (-62.5%)

Mutual labels: verilog

Busblaster

KT-Link compatible buffer for the Bus Blaster v3

Stars: ✭ 6 (-62.5%)

Mutual labels: verilog

Co4618

This repo is for the 4618 group nember to share code.

Stars: ✭ 5 (-68.75%)

Mutual labels: verilog

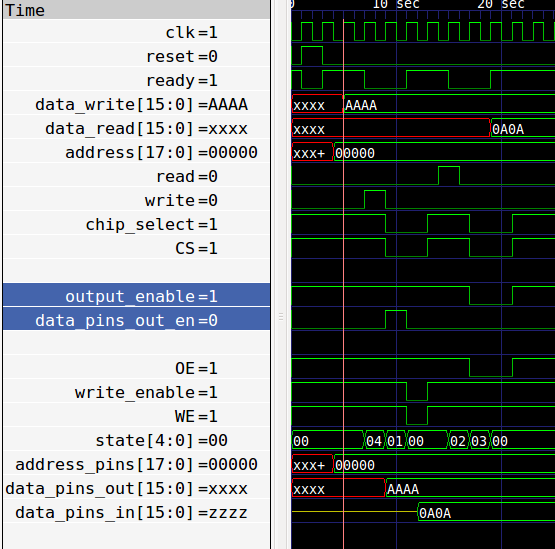

SRAM on the mystorm blackice

mystorm blackice has 0.5MByte SRAM on the back of the board

From datasheet: ISSI IS62WV25616DALL and IS62/65WV25616DBLL are high-speed, low power, 4M bit SRAMs organized as 256K words by 16 bits.

verilog

- extremely simple test of the SRAM

- state machine for read and write

- everything done in 1 cycle as 1 cycle at 12MHz is slower than max read/write time of the SRAM.

current status

- working at 12MHz system clock

- test reads then writes to first 2^16 words

- data written is the current address

- bits 14:11 of the data is shown on the boards's 4 leds

- boring test video

testbench

problems

2 pins on the data bus collide with pins of the PLLs. When the PLL is activated, those pins can no longer be inout, they must be either in or out. More details here

Note that the project description data, including the texts, logos, images, and/or trademarks,

for each open source project belongs to its rightful owner.

If you wish to add or remove any projects, please contact us at [email protected].