madcowswe / Odrivehardware

Licence: mit

High performance motor control

Stars: ✭ 498

Labels

Projects that are alternatives of or similar to Odrivehardware

Beagle sdr gps

KiwiSDR: BeagleBone web-accessible shortwave receiver and software-defined GPS

Stars: ✭ 300 (-39.76%)

Mutual labels: verilog

Leflow

Enabling Flexible FPGA High-Level Synthesis of Tensorflow Deep Neural Networks

Stars: ✭ 414 (-16.87%)

Mutual labels: verilog

Verilog Axi

Verilog AXI components for FPGA implementation

Stars: ✭ 349 (-29.92%)

Mutual labels: verilog

Openlane

OpenLANE is an automated RTL to GDSII flow based on several components including OpenROAD, Yosys, Magic, Netgen, Fault and custom methodology scripts for design exploration and optimization.

Stars: ✭ 293 (-41.16%)

Mutual labels: verilog

Vtr Verilog To Routing

Verilog to Routing -- Open Source CAD Flow for FPGA Research

Stars: ✭ 466 (-6.43%)

Mutual labels: verilog

Cascade

A Just-In-Time Compiler for Verilog from VMware Research

Stars: ✭ 413 (-17.07%)

Mutual labels: verilog

Scr1

SCR1 is a high-quality open-source RISC-V MCU core in Verilog

Stars: ✭ 393 (-21.08%)

Mutual labels: verilog

Reduceron

FPGA Haskell machine with game changing performance. Reduceron is Matthew Naylor, Colin Runciman and Jason Reich's high performance FPGA softcore for running lazy functional programs, including hardware garbage collection. Reduceron has been implemented on various FPGAs with clock frequency ranging from 60 to 150 MHz depending on the FPGA. A high degree of parallelism allows Reduceron to implement graph evaluation very efficiently. This fork aims to continue development on this, with a view to practical applications. Comments, questions, etc are welcome.

Stars: ✭ 308 (-38.15%)

Mutual labels: verilog

Sd2snes

SD card based multi-purpose cartridge for the SNES

Stars: ✭ 418 (-16.06%)

Mutual labels: verilog

Verilog

Repository for basic (and not so basic) Verilog blocks with high re-use potential

Stars: ✭ 296 (-40.56%)

Mutual labels: verilog

Microwatt

A tiny Open POWER ISA softcore written in VHDL 2008

Stars: ✭ 383 (-23.09%)

Mutual labels: verilog

Platformio Atom Ide

PlatformIO IDE for Atom: The next generation integrated development environment for IoT

Stars: ✭ 475 (-4.62%)

Mutual labels: verilog

Open Fpga Verilog Tutorial

Learn how to design digital systems and synthesize them into an FPGA using only opensource tools

Stars: ✭ 464 (-6.83%)

Mutual labels: verilog

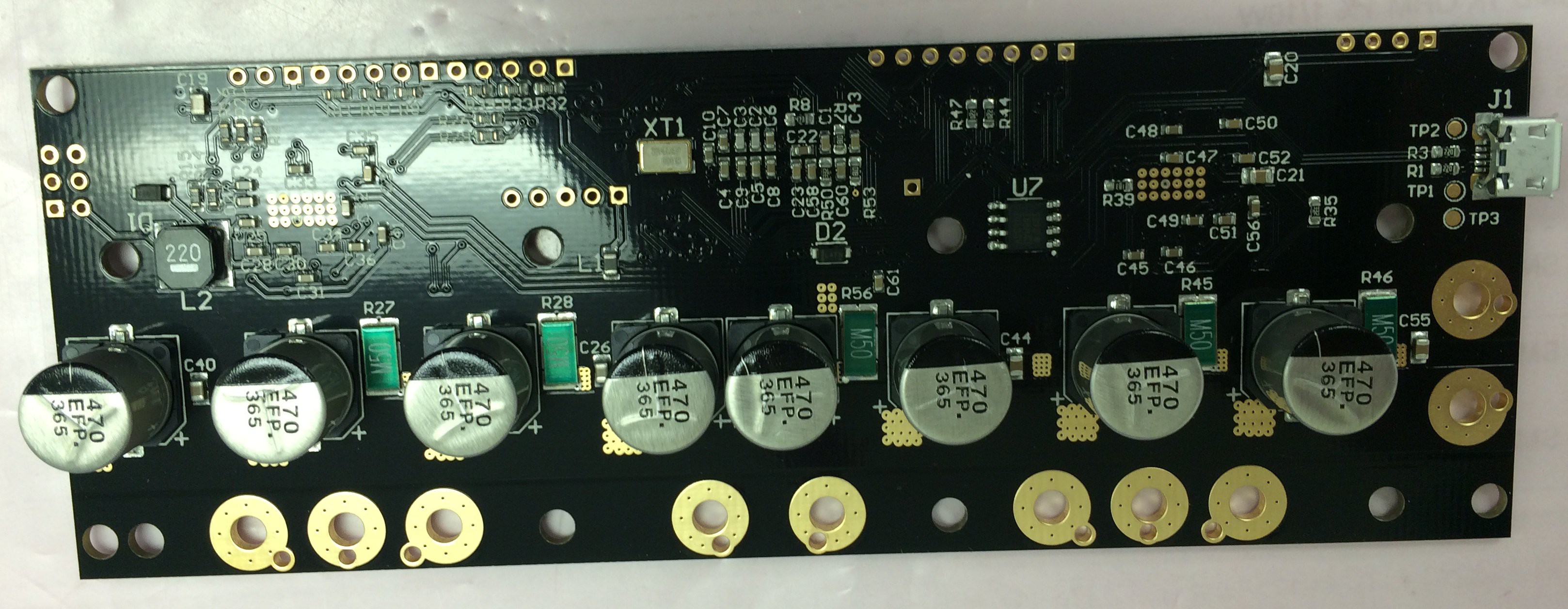

ODriveHardware

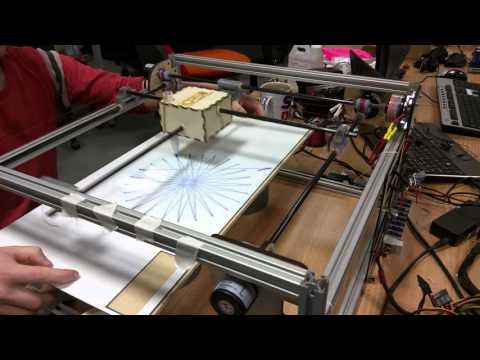

This project is all about accuratly driving brushless motors, for cheap. The aim is to make it possible to use inexpensive brushless motors in high performance robotics projects.

Like this (click for video):

If you want to get your hands on a board, check out this post.

This repository contains the circuit board design of ODrive. The other related repositories are:

- ODriveFirmware: Firmware that runs on the board.

- ODrive: Configuration and analysis scripts that runs on a PC.

There is also ODriveFPGA, which contains the FPGA logic and software that runs on the FPGA based ODrive. This is not currently in development, but may be resumed at some later date.

Odrive v3 board

The pinout from the microcontroller to the board is documented here.

Pictures!

ODrive v3.1 errata

- The silkscreen labels for the encoders (M0, M1) are reversed.

- The output impedence of the current amplifiers were not considered when designing the post-amplifier filters. Hence the response is about 5x slower than designed. Max allowed modulation index is therefore about 50%.

Note that the project description data, including the texts, logos, images, and/or trademarks,

for each open source project belongs to its rightful owner.

If you wish to add or remove any projects, please contact us at [email protected].