Darkriscvopensouce RISC-V cpu core implemented in Verilog from scratch in one night!

Stars: ✭ 1,062 (+2428.57%)

Mutual labels: cpu, riscv, risc-v

Riscv FsF# RISC-V Instruction Set formal specification

Stars: ✭ 173 (+311.9%)

Mutual labels: cpu, riscv, risc-v

Ustc RvsocFPGA-based RISC-V CPU+SoC.

Stars: ✭ 77 (+83.33%)

Mutual labels: cpu, riscv, risc-v

KyogenRVThe Simple 5-staged pipeline RISC-V written in chisel3 for intel FPGA.

Stars: ✭ 37 (-11.9%)

Mutual labels: riscv, chisel3, risc-v

Neorv32A small and customizable full-scale 32-bit RISC-V soft-core CPU and SoC written in platform-independent VHDL.

Stars: ✭ 106 (+152.38%)

Mutual labels: cpu, riscv, risc-v

Riscv RustRISC-V processor emulator written in Rust+WASM

Stars: ✭ 253 (+502.38%)

Mutual labels: cpu, riscv, risc-v

Zelda.RISCV.EmulatorA System Level RISCV32 Emulator Over x86_64: capable of booting RISCV Linux

Stars: ✭ 18 (-57.14%)

Mutual labels: riscv, risc-v

RiscboyPortable games console, designed from scratch: CPU, graphics, PCB, and the kitchen sink

Stars: ✭ 103 (+145.24%)

Mutual labels: cpu, risc-v

nuclei-sdkNuclei RISC-V Software Development Kit

Stars: ✭ 65 (+54.76%)

Mutual labels: riscv, risc-v

Awesome CpusAll CPU and MCU documentation in one place

Stars: ✭ 1,602 (+3714.29%)

Mutual labels: cpu, risc-v

E200 opensourceThis repository hosts the project for open-source hummingbird E203 RISC processor Core.

Stars: ✭ 1,909 (+4445.24%)

Mutual labels: cpu, risc-v

Rv12RISC-V CPU Core

Stars: ✭ 162 (+285.71%)

Mutual labels: cpu, risc-v

Cva6The CORE-V CVA6 is an Application class 6-stage RISC-V CPU capable of booting Linux

Stars: ✭ 1,144 (+2623.81%)

Mutual labels: cpu, riscv

platform-shaktiShakti: development platform for PlatformIO

Stars: ✭ 26 (-38.1%)

Mutual labels: riscv, risc-v

Mipt MipsCycle-accurate pre-silicon simulator of RISC-V and MIPS CPUs

Stars: ✭ 250 (+495.24%)

Mutual labels: cpu, risc-v

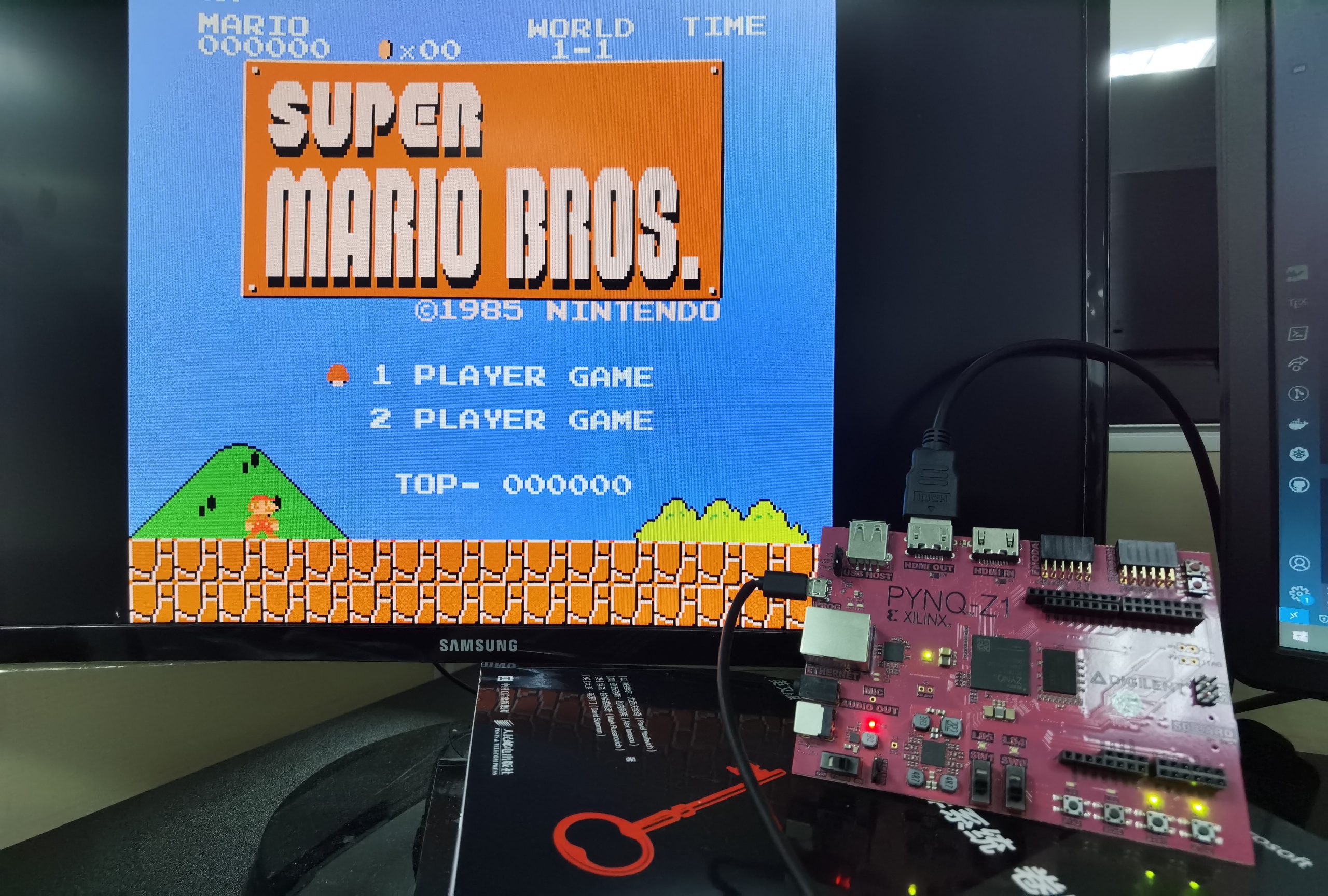

kianRiscVKianRISC-V! No RISC-V, no fun! RISC-V CPU with strong design rules and unittested! CPU you can trust! kianv rv32im risc-v a hdmi soc with harris computer architecture in verilog: multicycle, singlecycle and 5-stage pipelining Processor. Multicycle Soc with firmware that runs raytracer, mandelbrot, 3d hdmi gfx, dma controller, etc.....

Stars: ✭ 167 (+297.62%)

Mutual labels: cpu, riscv

VexriscvA FPGA friendly 32 bit RISC-V CPU implementation

Stars: ✭ 1,041 (+2378.57%)

Mutual labels: cpu, riscv

riscv-metaRISC-V Instruction Set Metadata

Stars: ✭ 33 (-21.43%)

Mutual labels: riscv, risc-v

Riscv vhdlPortable RISC-V System-on-Chip implementation: RTL, debugger and simulators

Stars: ✭ 356 (+747.62%)

Mutual labels: cpu, riscv

UnicornUnicorn CPU emulator framework (ARM, AArch64, M68K, Mips, Sparc, PowerPC, RiscV, X86)

Stars: ✭ 4,934 (+11647.62%)

Mutual labels: cpu, riscv