ultraembedded / Riscv

Licence: bsd-3-clause

RISC-V CPU Core (RV32IM)

Stars: ✭ 272

Projects that are alternatives of or similar to Riscv

Biriscv

32-bit Superscalar RISC-V CPU

Stars: ✭ 208 (-23.53%)

Mutual labels: verilog, fpga, cpu, risc-v, asic

Logic

CMake, SystemVerilog and SystemC utilities for creating, building and testing RTL projects for FPGAs and ASICs.

Stars: ✭ 149 (-45.22%)

Mutual labels: verilog, fpga, asic, verification

Darkriscv

opensouce RISC-V cpu core implemented in Verilog from scratch in one night!

Stars: ✭ 1,062 (+290.44%)

Mutual labels: verilog, fpga, cpu, risc-v

Aes

Verilog implementation of the symmetric block cipher AES (Advanced Encryption Standard) as specified in NIST FIPS 197. This implementation supports 128 and 256 bit keys.

Stars: ✭ 131 (-51.84%)

Mutual labels: verilog, fpga, asic

E200 opensource

This repository hosts the project for open-source hummingbird E203 RISC processor Core.

Stars: ✭ 1,909 (+601.84%)

Mutual labels: verilog, cpu, risc-v

kianRiscV

KianRISC-V! No RISC-V, no fun! RISC-V CPU with strong design rules and unittested! CPU you can trust! kianv rv32im risc-v a hdmi soc with harris computer architecture in verilog: multicycle, singlecycle and 5-stage pipelining Processor. Multicycle Soc with firmware that runs raytracer, mandelbrot, 3d hdmi gfx, dma controller, etc.....

Stars: ✭ 167 (-38.6%)

Mutual labels: cpu, fpga, verilog

VGChips

Video Game custom chips reverse-engineered from silicon

Stars: ✭ 86 (-68.38%)

Mutual labels: asic, fpga, verilog

spu32

Small Processing Unit 32: A compact RV32I CPU written in Verilog

Stars: ✭ 51 (-81.25%)

Mutual labels: fpga, verilog, risc-v

Open Register Design Tool

Tool to generate register RTL, models, and docs using SystemRDL or JSpec input

Stars: ✭ 126 (-53.68%)

Mutual labels: verilog, fpga, asic

Livehd

Live Hardware Development (LiveHD), a productive infrastructure for Synthesis and Simulation

Stars: ✭ 110 (-59.56%)

Mutual labels: verilog, fpga, asic

riscv-cores-list

RISC-V Cores, SoC platforms and SoCs

Stars: ✭ 651 (+139.34%)

Mutual labels: asic, fpga, risc-v

async fifo

A dual clock asynchronous FIFO written in verilog, tested with Icarus Verilog

Stars: ✭ 117 (-56.99%)

Mutual labels: fpga, verification, verilog

getting-started

List of ideas for getting started with TimVideos projects

Stars: ✭ 50 (-81.62%)

Mutual labels: fpga, verilog, risc-v

Rggen

Code generation tool for configuration and status registers

Stars: ✭ 54 (-80.15%)

Mutual labels: verilog, fpga, asic

drec-fpga-intro

Materials for "Introduction to FPGA and Verilog" at MIPT DREC

Stars: ✭ 66 (-75.74%)

Mutual labels: fpga, verilog, risc-v

RISC-V Core

Github: http://github.com/ultraembedded/riscv

A 32-bit RISC-V core written in Verilog and an instruction set simulator supporting RV32IM.

This core has been tested against a co-simulation model and exercised on FPGA.

For a higher performance dual issue CPU with branch prediction, see my latest RISC-V core here; http://github.com/ultraembedded/biriscv

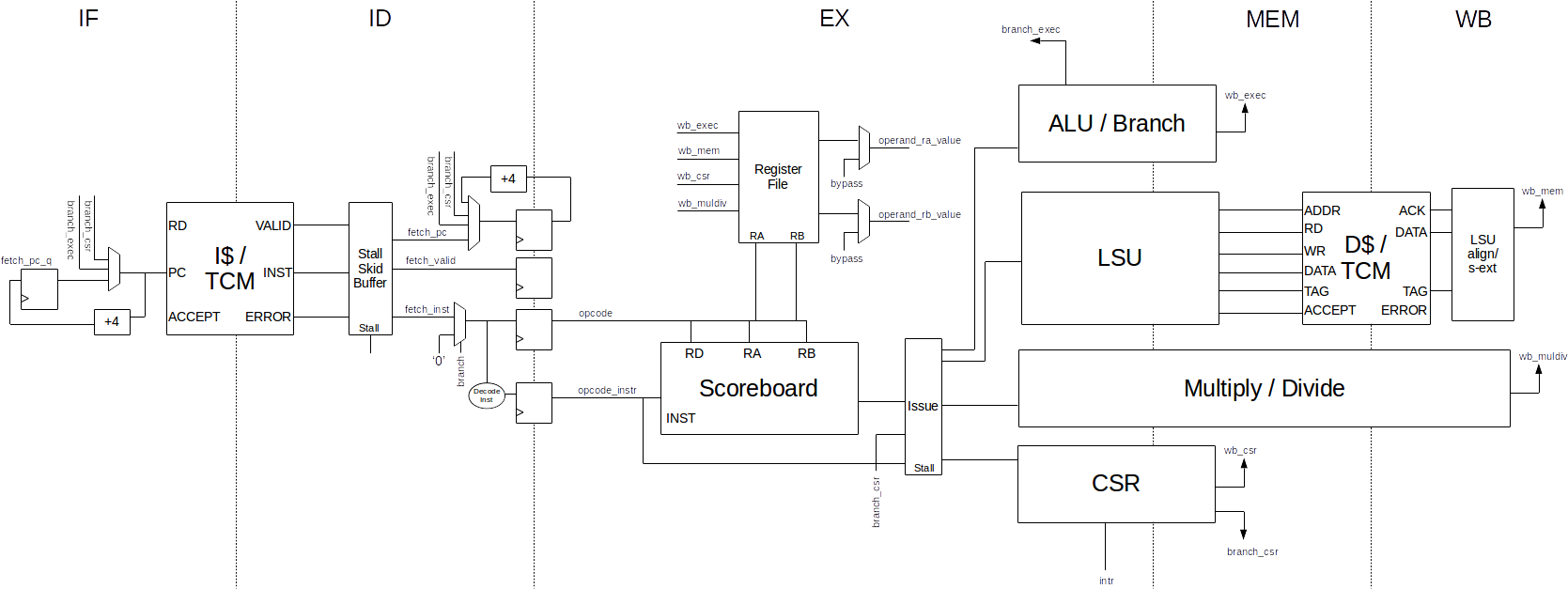

Overview

Features

- 32-bit RISC-V ISA CPU core.

- Support RISC-V integer (I), multiplication and division (M), and CSR instructions (Z) extensions (RV32IMZicsr).

- Supports user, supervisor and machine mode privilege levels.

- Basic MMU support - capable of booting Linux with atomics (RV-A) SW emulation.

- Implements base ISA spec v2.1 and privileged ISA spec v1.11.

- Verified using Google's RISCV-DV random instruction sequences using cosimulation against C++ ISA model.

- Support for instruction / data cache, AXI bus interfaces or tightly coupled memories.

- Configurable number of pipeline stages and result forwarding options.

- Synthesizable Verilog 2001, Verilator and FPGA friendly.

- Coremark: 2.94 CoreMark/MHz

- Dhrystone: 1.25 DMIPS/MHz ('legal compile options' / 337 instructions per iteration)

- Want higher performance (4.1CM/MHz / 1.9DMIPS/MHz) - see my improved core.

Configuration

| Param Name | Valid Range | Description |

|---|---|---|

| SUPPORT_SUPER | 1/0 | Enable supervisor / user privilege levels. |

| SUPPORT_MMU | 1/0 | Enable basic memory management unit. |

| SUPPORT_MULDIV | 1/0 | Enable HW multiply / divide (RV-M). |

| SUPPORT_LOAD_BYPASS | 1/0 | Support load result bypass paths. |

| SUPPORT_MUL_BYPASS | 1/0 | Support multiply result bypass paths. |

| SUPPORT_REGFILE_XILINX | 1/0 | Support Xilinx optimised register file. |

| EXTRA_DECODE_STAGE | 1/0 | Extra decode pipe stage for improved timing. |

| MEM_CACHE_ADDR_MIN | 32'h0 - 32'hffffffff | Lowest cacheable memory address. |

| MEM_CACHE_ADDR_MAX | 32'h0 - 32'hffffffff | Highest cacheable memory address. |

Directories

| Name | Contents |

|---|---|

| core/riscv | RISC-V pipelined RV32IM CPU core (Verilog) |

| isa_sim | Instruction set simulator (C) |

| top_tcm_axi/src_v | Example instance with 64KB DP-RAM & AXI Interfaces |

| top_tcm_axi/tb | System-C testbench for the core |

| top_cache_axi/src_v | Example instance with instruction and data caches. |

| top_cache_axi/tb | System-C testbench for the core |

Example Core Instance (with TCM memory)

The top (top_tcm_axi/src_v/riscv_tcm_top.v) contains;

- Instances one of the above cores, adding RAM and standard bus interfaces.

- 64KB dual ported RAM for (I/D code and data).

- AXI4 slave port for loading the RAM, DMA access, etc (including support for burst access).

- AXI4-Lite master port for CPU access to peripherals.

- Separate reset for CPU core to dual ported RAM / AXI interface (to allow program code to be loaded prior to CPU reset de-assertion).

Memory Map

| Range | Description |

|---|---|

| 0x0000_0000 - 0x0000_ffff | 64KB TCM Memory |

| 0x0000_2000 | Boot address (configurable, see RISCV_BOOT_ADDRESS) |

| 0x8000_0000 - 0xffff_ffff | Peripheral address space (from AXI4-L port) |

Interfaces

| Name | Description |

|---|---|

| clk_i | Clock input |

| rst_i | Async reset, active-high. Reset memory / AXI interface. |

| rst_cpu_i | Async reset, active-high. Reset CPU core (excluding AXI / memory). |

| axi_t_* | AXI4 slave interface for access to 64KB TCM memory. |

| axi_i_* | AXI4-Lite master interface for CPU access to peripherals. |

| intr_i | Active high interrupt input (for connection external int controller). |

Testbench

A basic System-C / Verilator based testbench for the core is provided.

Dependencies;

- gcc

- make

- libelf

- System-C (specify path using SYSTEMC_HOME)

- Verilator (specify path using VERILATOR_SRC)

To build the testbench;

cd top_tcm_axi/tb

make

To run the provided test executable;

cd top_tcm_axi/tb

make run

Example Core Instance (with caches)

The top (top_cache_axi/src_v/riscv_top.v) contains;

- Instances one of the above cores, adding RAM and standard bus interfaces.

- 16KB 2-way set associative instruction cache

- 16KB 2-way set associative data cache with write-back and allocate on write.

- 2 x AXI4 master port for CPU access to instruction / data / peripherals.

Interfaces

| Name | Description |

|---|---|

| clk_i | Clock input |

| rst_i | Async reset, active-high. Reset memory / AXI interface. |

| axi_i_* | AXI4 master interface for CPU access to instruction memory. |

| axi_d_* | AXI4 master interface for CPU access to data / peripheral memories. |

| intr_i | Active high interrupt input (for connection external int controller). |

| reset_vector_i | Boot vector. |

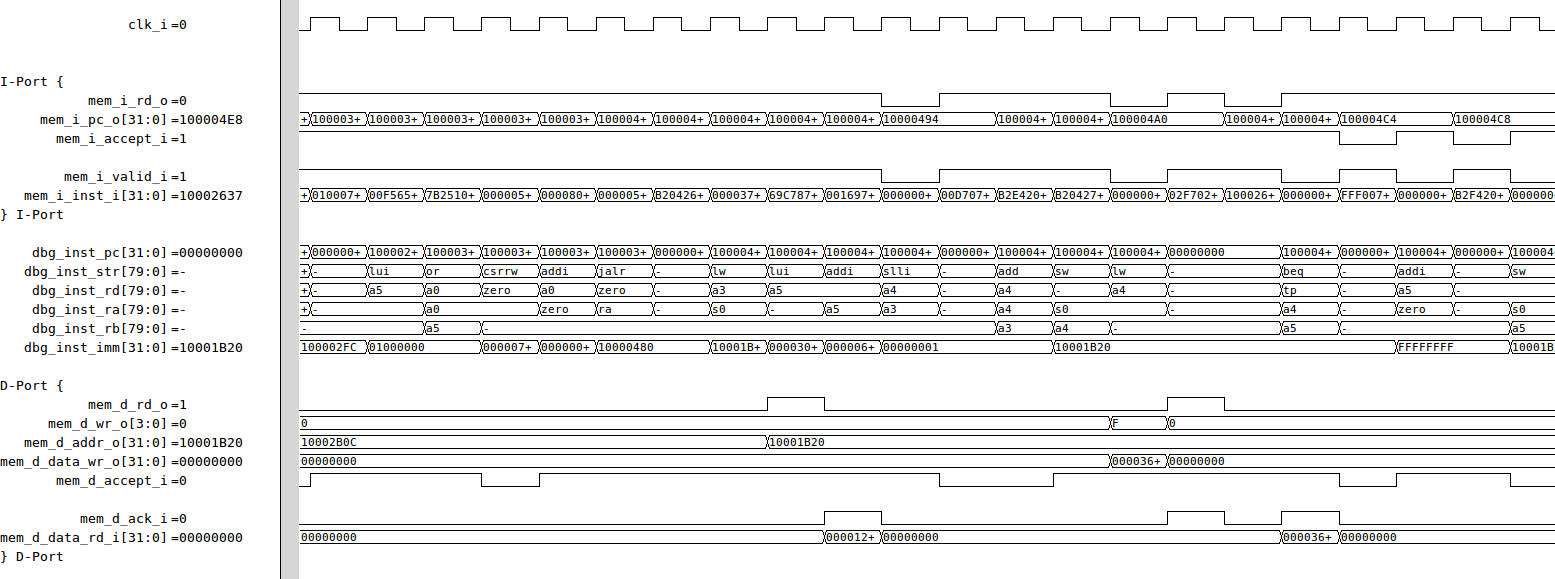

Execution Example

Note that the project description data, including the texts, logos, images, and/or trademarks,

for each open source project belongs to its rightful owner.

If you wish to add or remove any projects, please contact us at [email protected].